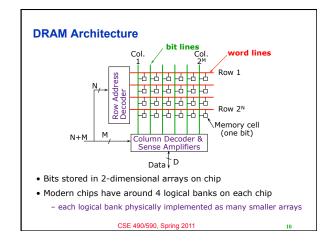

## **DRAM Operation**

Three steps in read/write access to a given bank

- Row access (RAS)

- decode row address, enable addressed row (often multiple Kb in row) stillnes share charge with storage cell small change in voltage detected by sense amplifiers which latch whole

- row of bits sense amplifiers drive bitlines full rail to recharge storage cells

- Column access (CAS)

- \_

- DIUMIN access (CAS) decode column address to select small number of sense amplifier latches (4, 8, 16, or 32 bits depending on DRAM package) on read, send latched bits out to chip pins on write, change sense amplifier latches which then charge storage cells to required value can perform multiple column accesses on same row without another row access (burst mode) recharge

- Precharge charges bit lines to known value, required before next row access

Each step has a latency of around 15-20ns in modern DRAMs Various DRAM standards (DDR, RDRAM) have different ways of encoding the signals for transmission to the DRAM, but all share same core architecture

11

CSE 490/590, Spring 2011

Time

## **Replacement Policy**

In an associative cache, which block from a set should be evicted when the set becomes full?

- Random

- Least Recently Used (LRU) • LRU cache state must be updated on every access • true implementation only feasible for small sets (2-way) • pseudo-LRU binary tree often used for 4-8 way

- First In, First Out (FIFO) a.k.a. Round-Robin

used in highly associative caches

- Not Least Recently Used (NLRU)

FIFO with exception for most recently used block or blocks

This is a second-order effect. Why?

Replacement only happens on misses

CSE 490/590, Spring 2011 34

- These slides heavily contain material developed and copyright by

- Krste Asanovic (MIT/UCB)David Patterson (UCB)

- David Patterson

- And also by:

Arvind (MIT)

- Joel Emer (Intel/MIT)

- James Hoe (CMU)

- John Kubiatowicz (UCB)

- MIT material derived from course 6.823

- UCB material derived from course CS252

CSE 490/590, Spring 2011

35