## **Conservative O-o-O Load Execution**

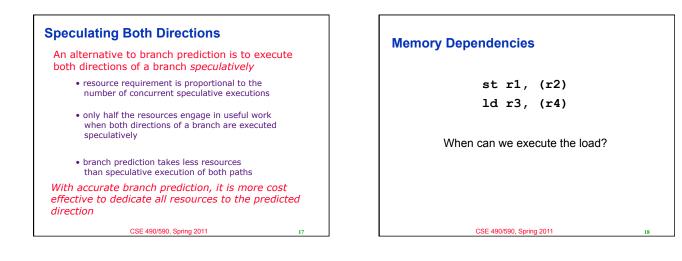

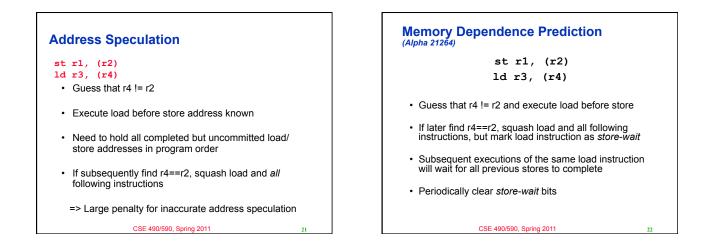

## st r1, (r2) ld r3, (r4)

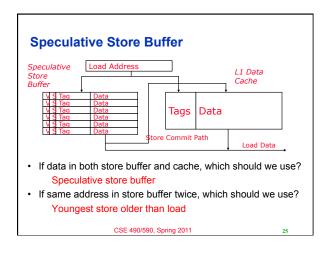

- Split execution of store instruction into two phases: address calculation and data write

- Can execute load before store, if addresses known and r4 != r2

- Each load address compared with addresses of all previous uncommitted stores (can use partial conservative check i.e., bottom 12 bits of address)

- · Don't execute load if any previous store address not known

(MIPS R10K, 16 entry address queue)

CSE 490/590, Spring 2011

## **Acknowledgements**

- These slides heavily contain material developed and copyright by

- Krste Asanovic (MIT/UCB)

- David Patterson (UCB)

- And also by:

Arvind (MIT)

- Joel Emer (Intel/MIT)

- James Hoe (CMU)

- John Kubiatowicz (UCB)

- MIT material derived from course 6.823

- UCB material derived from course CS252

CSE 490/590, Spring 2011

27